반도체 산업은 지속적인 혁신의 역사를 가지고 있으며, 그 중심에는 미세화 기술이 자리 잡고 있습니다. 하지만 물리적 한계에 도달함에 따라, 반도체 기술은 새로운 방향으로 나아가고 있습니다. 바로 3D 적층 기술입니다. 이 기술은 여러 칩을 층층이 쌓아 올려 하나의 통합된 시스템을 구성하는 것을 말합니다. 이러한 3D 패키징 기술은 TSMC가 선도하고 있는 분야로, 그들의 혁신적인 접근 방식은 업계 전반에 걸쳐 주목을 받고 있습니다.

3D 적층 기술

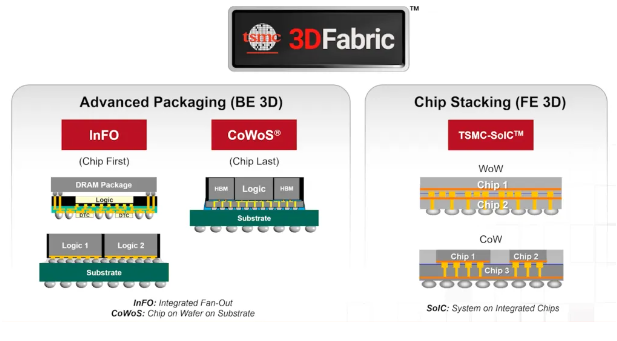

TSMC(Taiwan Semiconductor Manufacturing Company)는 세계 최대의 독립 반도체 파운드리(위탁생산업체)입니다. TSMC는 고객사의 설계에 따라 반도체를 제조해 주는 업체로, 다양한 기술 혁신을 통해 반도체 생산의 효율성과 성능을 지속적으로 개선하고 있습니다. 3D 적층 기술은 반도체 칩의 성능과 효율성을 극대화하기 위한 기술 중 하나입니다. 기존의 2D 평면적인 반도체 설계와 다르게, 3D 적층 기술은 여러 층의 반도체 소자들을 수직으로 쌓아 올리는 방식입니다. 이를 통해 칩의 크기를 줄이면서도 더 많은 기능을 포함시킬 수 있으며, 데이터 전송 속도도 크게 향상할 수 있습니다.

TSMC의 기술

InFO (Integrated Fan-Out) : InFO는 고밀도 RDL(Re-Distribution Layer)과 TIV(Through InFO Via)를 특징으로 하는 혁신적인 웨이퍼 레벨 시스템 통합 기술 플랫폼입니다. 이는 모바일, 고성능 컴퓨팅 등 다양한 애플리케이션에 대한 고밀도 인터커넥트와 성능을 제공합니다1. InFO 기술은 패키지 두께를 최대 20% 줄이고, 속도를 20% 향상하며, 전력 소비를 10% 개선할 수 있다고 합니다.

CoWoS (Chip on Wafer on Substrate) : CoWoS는 칩을 웨이퍼에 적층한 다음 기판에 패키징하여 2.5D 또는 3D 구성을 만드는 기술입니다. 이 방식은 칩 공간을 줄이고 전력 소비 및 비용을 낮추는 동시에, 고성능 컴퓨팅(HPC), AI, 데이터 센터, 5G, IoT, 자동차 전자 장치 등 다양한 분야에 응용됩니다.

SoIC (System on Integrated Chips) : SoIC는 마이크로 범프 없이 TSV(Through-Silicon Vias)로 칩을 쌓거나 고속 연결층을 넣어 다른 칩들을 연결하는 기술입니다. 이는 패키지 크기를 줄이고 성능을 향상하며, 이기종 Chiplet 통합 분야를 발전시키는 핵심 기술로, 더 작고, 더 좋은 성능, 더 낮은 전력 및 대기시간의 효율적인 칩 설계가 가능합니다.

중요성

이 기술은 단순히 칩의 크기를 줄이는 것에 그치지 않습니다. 3D 적층 기술은 반도체의 성능과 전력 효율을 획기적으로 높일 수 있는 가능성을 제시합니다. TSMC는 이 기술을 제품에 적용하여 양산을 하고 있으며, 이는 패키징 기술 발전을 가속화할 것으로 보입니다. 다른 주요 반도체 기업들도 이 분야에서 경쟁하며, 패키징 시장에서의 경쟁력을 높이고 있습니다. 업계 관계자들은 반도체 기업 간 패키징 기술 사이에는 구조적인 차이가 있지만, 칩 간 거리를 줄여 성능을 개선한다는 지향점은 동일하다고 평가하고 있습니다.

TSMC의 3D 적층 기술은 반도체 산업의 미래를 재정의할 수 있는 획기적인 발전입니다. 이 기술은 더 작고, 더 빠르며, 더 효율적인 칩을 만들어내며, 우리의 일상생활에 광범위한 영향을 미칠 것입니다. TSMC의 지속적인 혁신과 업계의 경쟁은 반도체 기술의 새로운 지평을 열고 있으며, 우리는 이러한 발전을 주목해야 할 것입니다.