이 기술은 대부분의 반도체 집적회로(IC)에서 주로 사용되는 중요 기술 중 하나이며, 소비전력이 낮고 뛰어난 신호 대 잡음 비율, 빠른 속도등 성능이 우수하여 다양한 전자기기에서 활용되고 있습니다. 이번 포스팅에서는 반도체 CMOS Well 디자인에 대해 알아보겠습니다.

CMOS 기술의 기본

CMOS는 N형과 P형 트랜지스터의 결합으로 이루어져 있습니다. N형 트랜지스터는 음전하를 가진 전자를 이용하며, P형 트랜지스터는 양전하를 가진 양자를 이용합니다. 이 두 종류의 트랜지스터를 조합하여 전력 소비를 최소화하면서도 뛰어난 성능을 발휘합니다.

Well의 역할

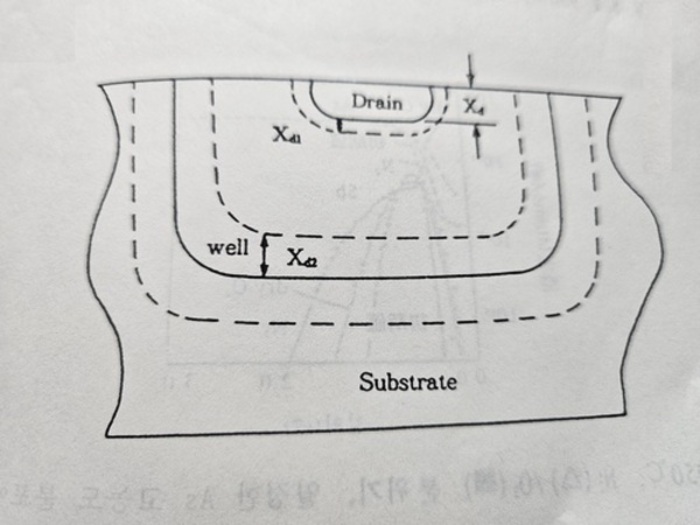

CMOS에는 하나의 n-MOSFET과 하나의 p-MOSFET이 들어가는데, 이 두 소자는 붙어있으면 전류가 누설되어 소자가 작동하지 않는 문제가 생길 수 있습니다. 그래서 CMOS를 만들기 위해서는 n-MOSFET과 p-MOSFET을 공간적으로 분리해주는 Well을 형성해야 합니다. Well이란 Sub에 도핑된 영역을 말하는데, n-MOSFET은 p-type의 Well에, p-MOSFET은 n-type의 Well에 형성됩니다. 이를 각각 p-well과 n-well이라고 부릅니다. 이 영역은 트랜지스터 간의 간섭을 최소화하고 전기적인 분리를 유지하여 전자기기의 안정성과 성능을 향상시킵니다. Well을 형성하는 방법에는 여러 가지가 있지만, 가장 일반적인 방법은 n-well CMOS 공정입니다. n-well CMOS 공정은 p-type의 기판(웨이퍼)에 n-well을 형성하고, 그 안에 p-MOSFET을 만드는 공정입니다.

P-well 및 N-welll 디자인

P-well과 N-well은 각각 N형 및 P형 트랜지스터를 위한 지역을 나타냅니다. 이 두 Well은 서로 다른 전하를 가지고 있어 소자의 기능을 조절하고 전력 효율성을 높이는 데 기여합니다.

Well의 깊이 및 넓이

Well의 깊이와 넓이는 전체 칩의 레이아웃에 영향을 주며 트랜지스터의 특성을 결정하는 중요한 변수입니다. 깊이가 깊을수록 전하간의 상호 작용이 줄어들어 안정성이 증가하며, 넓이가 충분히 확보되면 트랜지스터 간의 간섭을 최소화할 수 있습니다.

Well의 절연

Well은 절연 층에 의해 감싸져 있어 서로 다른 전하를 가진 영역 간의 상호 간섭을 방지합니다. 이를 통해 소자의 성능을 안정화시키고 전력 효율성을 높입니다.

전기 및 열 특성

Well 디자인은 전기적 특성에 큰 영향을 있으므로, 적절한 Well 디자인은 MOSFET의 효율적인 동작에 영향을 미칩니다. 반도체 소자는 고온에서도 안정적으로 동작이 해야 하므로, Well 디자인은 고온에서의 안정성을 고려하여야 합니다.

최근의 발전과 미래 전망

최근에는 미세화 공정 기술과 3차원적인 구조를 활용하여 CMOS Well 디자인이 계속해서 발전하고 있습니다. 이러한 발전은 더 작고 효율적인 전자기기의 제작을 가능케 하며, 미래에는 더욱 높은 집적도와 성능을 갖춘 반도체 제품 생산이 가능합니다.

CMOS Well 디자인은 반도체 핵심 기술 중 하나로, 전기적, 열적 측면을 고려해 디자인 해야 안정성과 효율성 높은 디바이스를 생산 할 수 있습니다. 끊임없이 개선하고 있는 기술은 더 나은 전자 제품의 개발을 이끌어내며, 미래 기술 발전에 기여합니다.