이번 포스팅에는 반도체 CMOS Interconnect에 대해 자세히 알아보겠습니다. 반도체 칩은 수십억 개의 트랜지스터로 구성되어 있습니다. 트랜지스터는 전기적 신호를 증폭하거나 스위칭하는 역할을 합니다. 하지만 트랜지스터만으로는 원하는 기능을 수행할 수 없습니다. 트랜지스터들을 적절하게 연결하여 회로를 구성해야 합니다. 이때 트랜지스터들을 연결하는 전선을 Interconnect라고 부릅니다.

Interconnect는 반도체 칩의 성능과 전력 소모에 큰 영향을 미칩니다. Interconnect의 길이와 저항이 커지면 신호의 지연과 감쇠가 발생하고, 전력 손실이 증가합니다. 또한 Interconnect 사이의 간섭이나 누설 전류도 문제가 될 수 있습니다. 따라서 Interconnect의 설계와 최적화는 반도체 기술의 중요한 주제입니다.

중요성

신호를 전달하고 전류가 흐를 수 있도록 하는 핵심 역할을 합니다. 이를 통해 반도체 소자들 간에 효율적으로 정보를 교환할 수 있습니다. 전기적 특성에 영향을 미치는데, 이는 저항, 용량, 인덕턴스 등을 최소화하여 전기적 성능을 최적화하는 것을 의미합니다. 고밀도 집적회로에서는 열 분산이 중요합니다. 전력 소비를 최소화하고 열이 효율적으로 분산되도록 하는 역할을 합니다.

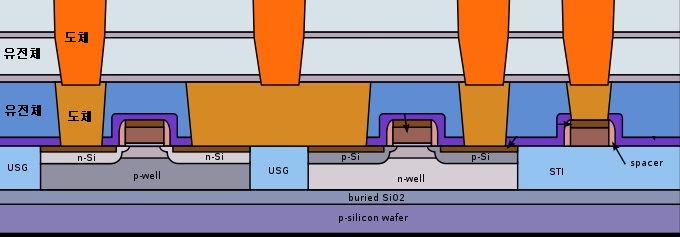

구조

도체와 유전체로 구성됩니다. 도체는 전기적 신호를 전달하는 역할을 하고, 유전체는 도체 사이의 절연과 전기적 특성을 개선하는 역할을 합니다. 도체로는 주로 Al이나 Cu와 같은 금속이 사용되고, 유전체로는 SiO2나 박막 등의 재료가 사용됩니다. 최근에는 카본 나노튜브와 같은 나노 기술이 도입되기도 합니다. 이러한 물질들은 낮은 저항과 용량을 가지며, 고주파에서도 안정적인 성능을 발휘합니다.

발전과 해결 사항

반도체 칩의 집적도와 성능을 향상시키기 위해 지속적으로 발전해왔습니다. Interconnect의 크기와 간격을 줄이고, 층 수를 늘리고, 새로운 재료와 공정을 도입하고, 구조와 설계를 개선하고, 신호 무결성과 전력 소모를 최적화하는 등의 노력이 이루어졌습니다. 그러나 더 이상 스케일링의 이점을 누리기 어려운 상황에 직면하고 있습니다. 크기와 간격이 줄어들면, 저항과 정전 용량이 증가하고, 신호의 지연과 감소가 심해지고, 전력 손실이 커지고, 간섭과 누설 전류가 문제가 됩니다. 또한 층 수가 늘어나면, 공정 복잡도와 비용이 증가하고, 신뢰성이 감소하고, 열 문제가 심화됩니다. 또한 새로운 재료와 공정의 도입에도 한계와 어려움이 있습니다.

전자 제품의 성능과 효율성을 결정짓는 중요한 요소입니다. 새로운 패러다임과 혁신이 필요한 시점으로 3차원 통합, 광 Interconnect, 나노물질, 인공지능 등의 새로운 기술과 끊임없이 발전하는 혁신적 기술로, 미래에는 더 높은 성능과 효율성을 갖춘 CMOS Interconnect이 반도체의 산적한 문제를 해결 할 수 있을 것입니다.