반도체 산업에서 3D 적층 기술은 혁신적인 발전을 의미합니다. 인텔은 이 분야의 선두 주자 중 하나로, 그들의 연구와 개발은 전자 제품의 성능 향상에 크게 기여하고 있습니다. 3D 적층 기술은 반도체 칩 내부에 트랜지스터를 수직으로 쌓아 올려 더 많은 기능을 소형 공간에 집약할 수 있게 해 줍니다. 이는 칩의 속도와 효율성을 향상하며, 에너지 소비를 줄이는 데에도 도움을 줍니다.

특징

전통적인 반도체 제조 기술은 2D 평면 위에 트랜지스터를 배치하는 방식에 의존해왔습니다. 하지만 물리적 한계에 도달함에 따라, 트랜지스터의 크기를 더 이상 줄이는 것이 어려워졌고, 이에 대한 해결책으로 3D 적층 기술이 주목받기 시작하였습니다. 인텔의 3D 적층 기술은 트랜지스터를 수직으로 쌓아 올리는 방식으로, 기존의 2D 플랜에 비해 훨씬 더 높은 집적도를 실현할 수 있으며, 이 기술의 가장 큰 장점은 공간 활용의 극대화에 있다. 3D 적층 기술을 통해, 인텔은 같은 면적 내에 더 많은 트랜지스터를 배치할 수 있게 되었다. 이는 곧 더 높은 성능과 에너지 효율성으로 이어진다. 또한, 인텔의 기술은 다양한 층에 서로 다른 기능을 갖는 트랜지스터를 배치할 수 있어, 기능적으로도 훨씬 더 다양한 반도체 칩의 설계가 가능해졌다.

Intel의 기술

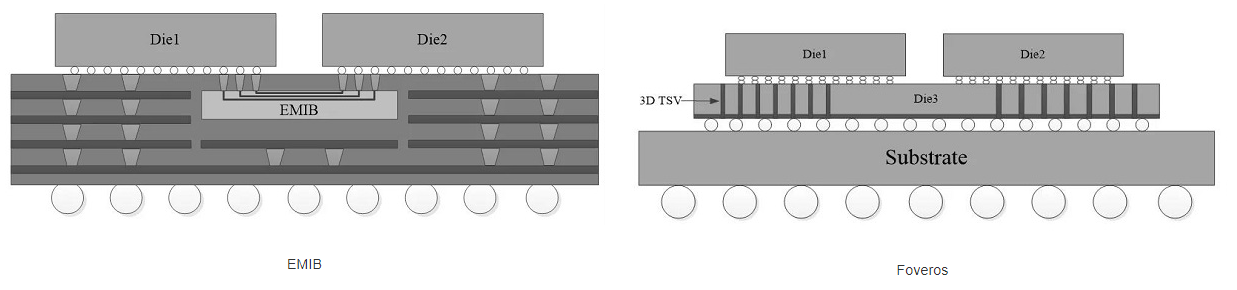

인텔의 3D 적층 기술은 크게 두 가지 주요 기술로 구분될 수 있습니다: EMIB(Embedded Multi-die Interconnect Bridge)와 Foveros입니다. 이 두 기술은 각각 다른 접근 방식과 응용 분야를 가지고 있으며, 인텔이 반도체 설계와 제조 분야에서 선도적인 위치를 유지할 수 있게 하는 중요한 요소입니다.

EMIB (Embedded Multi-die Interconnect Bridge)는 서로 다른 기술로 제작된 칩들을 하나의 패키지 내에서 연결하는 기술입니다. 이 방식은 특히 서로 다른 제조 공정으로 만들어진 칩들 사이에서 고속의 데이터 전송을 가능하게 합니다. 예를 들면, EMIB 기술을 사용하여 고성능 CPU와 고용량 메모리 칩을 하나의 패키지에 통합할 수 있습니다. EMIB는 실리콘 브리지를 사용하여 칩들 사이의 물리적 연결을 만듭니다. 이 브리지는 매우 높은 대역폭의 데이터 전송을 지원하며, 기존의 와이어 본딩(wire-bonding)이나 플립 칩(flip-chip) 방식보다 훨씬 더 효율적입니다.

Foveros는 수직 적층 기술로, 서로 다른 기능을 가진 여러 칩을 수직으로 쌓아 올리는 방식입니다. 이 기술을 통해, 인텔은 CPU, GPU, AI 프로세서 등 다양한 기능을 가진 칩을 하나의 패키지에 통합할 수 있습니다. 이러한 통합은 칩 간의 데이터 전송 속도를 향상시키고, 전력 소비를 줄이며, 전체 시스템의 크기를 줄일 수 있게 합니다. Foveros 기술의 핵심은 ‘액티브 인터포저(active interposer)’에 있습니다. 이는 칩 층 사이에 위치하며, 데이터와 전력을 전송하는 역할을 합니다. 액티브 인터포저를 사용함으로써, 인텔은 더 높은 데이터 전송 속도와 효율성을 달성할 수 있습니다.

도전 과제

더 많은 트랜지스터를 칩에 집약함으로써 발생하는 열 관리 문제가 있습니다. 인텔은 이 문제를 해결하기 위해 고급 냉각 기술을 개발하고 있으며, 이는 칩의 안정성과 수명을 보장하는 데 중요한 역할을 합니다.

인텔의 EMIB와 Foveros 기술은 각각 독특한 방식으로 3D 적층 기술을 활용하고 있습니다. EMIB는 다양한 기술로 제작된 칩들을 효율적으로 연결하며, Foveros는 칩의 수직 적층을 통해 공간 효율성을 극대화하합니다. 이 기술이 계속 발전함에 따라, 우리는 더 작고, 더 빠르며, 더 효율적인 전자 기기를 기대할 수 있습니다. 인텔의 혁신은 전 세계 기술 발전에 중대한 영향을 미치고 있으며, 앞으로도 그 영향력은 계속될 것입니다.